Tutorial Microcontroladores

Microcontroladores

Octal

Antes de comenzar la discusión sobre los sistemas de numeración y códigos, vimos dos códigos más respecto de los cuales podemos oír hablar. La notación octal (base 8) fue usada para trabajar con algunas computadoras primitivas, pero rara vez es utilizada en la actualidad. Esta usa los números que van del 0 al 7 para representar un conjunto de tres dígitos binarios de un modo análogo que en la hexadecimal se recurre a un conjunto de cuatro dígitos binarios. El sistema octal tiene la ventaja de no necesitar símbolos no numéricos (como los símbolos hexadecimales ya vistos, que van de la "A" a la "F").

Dos desventajas acarrea cambiar la notación haxadecimal usada hoy en día por la octal. La primera, de todas las computadoras, la mayoría utilizan "words" (palabras) de 4, 8, 16 ó 32 bits, estas "palabras" no resultan fácilmente fraccionables en grupos de tres bits (algunas computadoras muy antiguas usaban palabras de 12 bits siendo divisibles en cuatro grupos de tres bits). La segunda, es el hecho de carecer de la compactabilidad del hexadecimal. Por ejemplo, el valor ASCII de la letra "A" mayúscula es 10000001(2), 41(16) en hexadecimal y 101(8) en octal. Cuando una persona menciona el valor ASCII para la "A", es más fácil decir "cuarto - uno" que "uno - cero - uno".

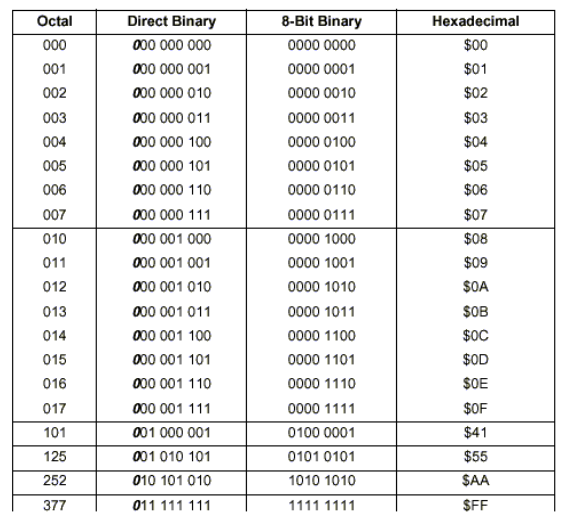

La tabla 2-3 presenta las correlaciones entre octal y binario. La columna "binario directo" muestra dígito por dígito el pasaje de los dígitos octales a grupos de 3 bits. El bit del extremo izquierdo (noveno) se ha resaltado. Este cero resaltado no es significativo para formar un resultado de ocho bits. La columna "8 bits binarios" contiene la misma información que la anterior salvo que están ordenados en grupos de 4 bits. Cada grupo de 4 bits se convierte directamente en un dígito hexadecinal.

Tabla 2-3 – Equivalentes Octal, Binario y Hexadecimal.

Cuando mentalmente convertimos valores octales a valores binarios de un byte, el valor octal resultante se representará mediante 3 dígitos octales. Cada dígito octal representa a su vez 3 bits con lo que resulta un bit extra (3 dígitos x 3 bits = 9 bits). Típicamente la gente opera de izquierda a derecha, lo que hace fácil olvidarse del tratamiento que debe recibir el bit extra del extremo izquierdo (noveno) de un octal. Cuando convertimos de hexadecimal a binario, nos resulta fácil puesto que cada dígito hexadecimal se transforma exactamente en cuatro bits. Dos dígitos hexadecimales coinciden exactamente con los ocho bits de un byte.

Binario Codificado en Decimal.

El sistema Binario Codificado en Decimal (BCD) es una notación híbrida usada para expresar valores decimales en forma binaria. Un BCD utiliza cuatro bits para representar cada dígito decimal.

De esta manera cuatro dígitos binarios pueden expresar 16 diferentes cantidades físicas, habiendo seis combinaciones consideradas no válidas (específicamente, los valores hexadecimales de la “A” a la “F”). Los valores BCD se representan con el signo “$”, pues ellos son números hexadecimales que representan cantidades decimales. Cuando la computadora hace una operación de suma BCD, ella realiza una suma binaria y luego realiza un ajuste que genera un resultado BCD. Como un simple ejemplo, consideremos la siguiente suma BCD.

9(10) + 1(10) = 10 (10)

donde (10), significa Base 10.

La computadora suma........

0000 1001(2)+0000 0001(2)=0000 1010(2)

donde (2), significa Base 2.

Pero 1010(2) es equivalente a “A(16)” que es un código BCD no válido. Cuando la computadora termina el cálculo, realiza un chequeo para ver si el resultado es un código BCD válido. Si hubo un “acarreo” (un desborde) de un dígito BCD a otro o si Hubiese algún código no válido, se desencadena una secuencia de etapas para corregir el resultado y llevarlo al formato BCD apropiado. El número 0000 1010(2) es corregido y se transforma en 0001 0000(2) (BCD 10) en este ejemplo.

Tabla 2-4 – Equivalentes Decimal, BCD, y Binario.

En la mayoría de los casos es ineficiente utilizar la notación BCD para los cálculos de la computadora. Es mejor convertir la información de decimal a binario en el momento de su ingreso, realizar todos los cálculos en binario y convertirlos nuevamente a BCD o decimal sólo si es necesario presentarlos en un exhibidor.

No todos los microcontroladores son capaces de realizar cálculos en BCD ya que necesitamos tener la indicación del acarreo dígito a dígito que no está presente en todas las computadoras (tener en cuenta que en los MCUs de Freescale tienen este indicador de semi-acarreo). Forzar a una computadora a comportarse como nosotros resulta menos eficiente que permitirle trabajar en su sistema de numeración natural.

Revisión del capítulo 2

Las computadoras aceptan dos niveles lógicos (0 y 1) con los que trabaja en el sistema de numeración binario. Las personas por tener diez dedos en las manos trabajan con el sistema de numeración decimal.

Los números hexadecimales utilizan dieciséis símbolos del 0 al 9 y de la A a la F. Cada dígito hexadecimal puede representarse mediante cuatro dígitos binarios. La tabla 2-1 nos muestra la equivalencia entre decimal, binario y hexadecimal de varios valores. Para poder distinguir un valor hexadecimal de otro decimal, colocaremos un símbolo $ antecediendo al hexadecimal.

El ASCII es un código ampliamente aceptado y nos permite representar tanto información alfanumérica como valores binarios.

Cada instrucción o variante de una instrucción posee un único código de operación (valor binario) que la CPU reconoce como un pedido para realizar una instrucción específica. Las CPUs de diferentes fabricantes poseen repertorios de códigos de operación distintos.

Los programadores explicitan instrucciones mediante un mnemónico tal como “INCA”. Un programa de computadora llamado ensamblador (ASSEMBLER COMPILER), traduce las instrucciones de mnemónicos a códigos de operación que la CPU puede reconocer.